- Each Device Drives 32 Lines

- 60-V Output Voltage Swing Capability

- 25-mA Output Source Current Capability

- High-Speed Serially Shifted Data Input

- Latches on All Driver Outputs

#### description

The SN65518 and SN75518 are monolithic BIDFET<sup>†</sup> integrated circuits designed to drive a dot matrix or segmented vacuum fluorescent display.

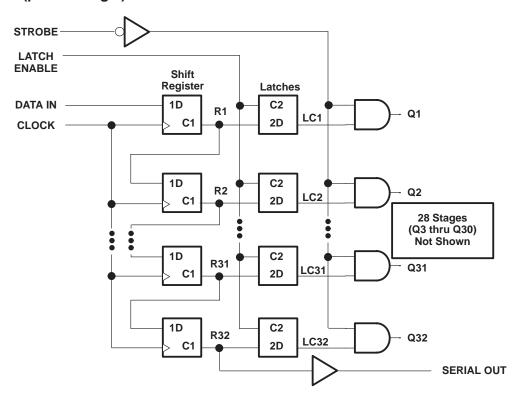

Each device consists of a 32-bit shift register, 32 latches, and 32 output AND gates. Serial data is entered into the shift register on the low-to-high transition of CLOCK. While LATCH ENABLE is high, parallel data is transferred to the output buffers through a 32-bit latch. Data present in the latch during the high-to-low transition of LATCH ENABLE is latched. When STROBE is low, all Q outputs are enabled. When STROBE is high, all Q outputs are low.

Serial data output from the shift register may be used to cascade additional devices. This output is not affected by LATCH ENABLE or STROBE.

The SN65518 is characterized for operation from –40°C to 85°C. The SN75518 is characterized for operation from 0°C to 70°C.

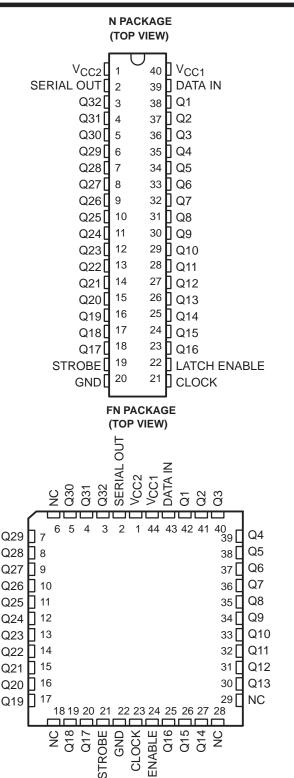

NC - No internal connection

†BIDFET – Bipolar, double-diffused, N-channel and P-channel MOS transistors on same chip. This is a patented process.

-ATCH

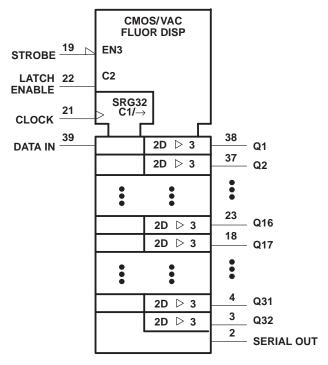

## logic symbol<sup>†</sup>

<sup>&</sup>lt;sup>†</sup> This symbol is in accordance with ANSI/IEEE Std 91-1984 and IEC Publication 617-12. Pin numbers shown are for the N package.

## logic diagram (positive logic)

# SN65518, SN75518 VACUUM FLUORESCENT DISPLAY DRIVERS

SLDS004B - MARCH 1983 - REVISED MAY 1990

#### **FUNCTION TABLE**

|          | CONTROL INPUTS |                 |        | SHIFT REGISTERS                          | LATCHES                     | OUTPUTS |                                      |  |

|----------|----------------|-----------------|--------|------------------------------------------|-----------------------------|---------|--------------------------------------|--|

| FUNCTION | CLOCK          | LATCH<br>ENABLE | STROBE | R1 THRU R32                              | LC1 THRU LC32               | SERIAL  | Q1 THRU Q32                          |  |

| Load     | ↑<br>No ↑      | X<br>X          | X<br>X | Load and shift <sup>†</sup><br>No change | Determined by LATCH ENABLE‡ | R32     | Determined by STROBE                 |  |

| Latch    | X<br>X         | L<br>H          | X<br>X | As determined above                      | Stored data<br>New data     | R32     | Determined by STROBE                 |  |

| Strobe   | X<br>X         | X<br>X          | H      | As determined above                      | Determined by LATCH ENABLE‡ | R32     | All L<br>LC1 thru LC32, respectively |  |

H = high level, L = low level, X = irrelevant,  $\uparrow = low-to-high-level transition$ .

# typical operating sequence

| CLOCK             |                        |                |

|-------------------|------------------------|----------------|

| DATA IN           | Valid                  | Irrelevant     |

|                   |                        |                |

| SR<br>Contents    | Invalid                | Valid          |

| LATCH<br>ENABLE   |                        |                |

|                   |                        |                |

| Latch<br>Contents | Previously Stored Data | New Data Valid |

|                   |                        |                |

| STROBE            |                        |                |

| Q Outputs         |                        | Valid          |

<sup>†</sup>R32 and the serial output take on the state of R31, R31 takes on the state of R30, ... R2 takes on the state of R1, and R1 takes on the state of the data input.

<sup>‡</sup> New data enter the latches while LATCH ENABLE is high. These data are stored while LATCH ENABLE is low.

SLDS004B - MARCH 1983 - REVISED MAY 1990

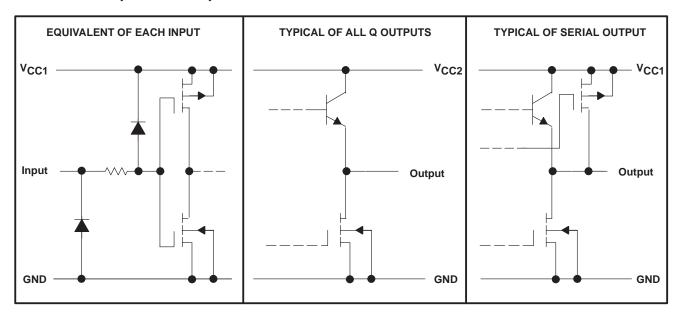

## schematic of inputs and outputs

## absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

| Supply voltage, V <sub>CC1</sub> (see Note 1)                  | 15 V                         |

|----------------------------------------------------------------|------------------------------|

| Supply voltage, V <sub>CC2</sub>                               | 70 V                         |

| Input voltage, V <sub>I</sub>                                  | V <sub>CC1</sub>             |

| Continuous total power dissipation                             | See Dissipation Rating Table |

| Operating free-air temperature range, T <sub>A</sub> : SN65518 | 8 −40°C to 85°C              |

| SN75518                                                        | 3 0°C to 70°C                |

| Storage temperature range, T <sub>stg</sub>                    | –65°C to 150°C               |

|                                                                | 260°C                        |

|                                                                | 10 seconds: N package        |

NOTE 1: Voltage values are with respect to network ground terminal.

#### **DISSIPATION RATING TABLE**

|   | $\begin{array}{cc} \text{PACKAGE} & \text{T}_{\text{A}} \leq 25^{\circ}\text{C} \\ \text{POWER RATING} \end{array}$ |         | DERATING FACTOR<br>ABOVE T <sub>A</sub> = 25°C | T <sub>A</sub> = 70°C<br>POWER RATING | T <sub>A</sub> = 85°C<br>POWER RATING |  |

|---|---------------------------------------------------------------------------------------------------------------------|---------|------------------------------------------------|---------------------------------------|---------------------------------------|--|

| ſ | FN                                                                                                                  | 1700 mW | 13.6 mW/°C                                     | 1088 mW                               | 884 mW                                |  |

| I | N                                                                                                                   | 1250 mW | 10.0 mW/°C                                     | 800 mW                                | 650 mW                                |  |

# recommended operating conditions, $T_A = 25$ °C (unless otherwise noted)

|                                                          |                                 | MIN  | MAX | UNIT |  |

|----------------------------------------------------------|---------------------------------|------|-----|------|--|

| Supply voltage, V <sub>CC1</sub>                         | 4.5                             | 15   | V   |      |  |

| Supply voltage, V <sub>CC2</sub>                         | 0                               | 60   | V   |      |  |

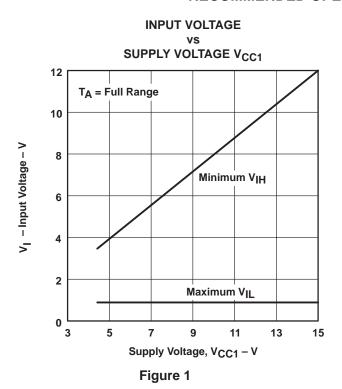

| High level input voltage VVV (acc Figure 1)              | V <sub>CC1</sub> = 4.5 V        | 3.5  |     | V    |  |

| High-level input voltage, V <sub>IH</sub> (see Figure 1) | V <sub>CC1</sub> = 15 V         | 12   |     | V    |  |

| Low-level input voltage, V <sub>IL</sub> (see Figure 1)  |                                 | -0.3 | 0.8 | V    |  |

| High-level output current, IOH                           |                                 |      |     | mA   |  |

| Low-level output current, IOL                            |                                 |      |     | mA   |  |

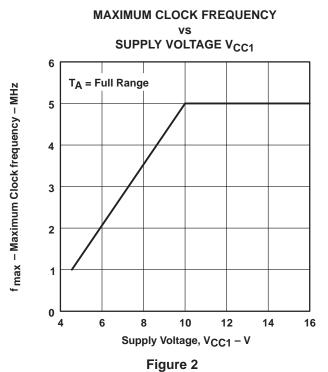

| Clock frequency, f <sub>clock</sub> (see Figure 2)       | V <sub>CC1</sub> = 10 V to 15 V | 0    | 5   | MHz  |  |

|                                                          | V <sub>CC1</sub> = 4.5 V        | 0    | 1   |      |  |

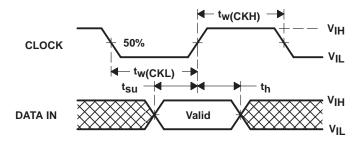

| Bulgo duration CLOCK high to court                       | V <sub>CC1</sub> = 10 V to 15 V | 100  |     | no   |  |

| Pulse duration, CLOCK high, t <sub>W</sub> (CKH)         | V <sub>CC1</sub> = 4.5 V        | 500  |     | ns   |  |

| Pulse duration, CLOCK low, tw(CKL)                       | V <sub>CC1</sub> = 10 V to 15 V | 100  |     | ne   |  |

| Fulse duration, GLOCK low, tw(CKL)                       | V <sub>CC1</sub> = 4.5 V        | 500  |     | ns   |  |

| Setup time, DATA IN before CLOCK↑, t <sub>SU</sub>       | V <sub>CC1</sub> = 10 V to 15 V | 75   |     | ns   |  |

| Setup time, DATA IN Delote CLOCKT, ISU                   | V <sub>CC1</sub> = 4.5 V        | 150  |     |      |  |

| Hold time, DATA IN after CLOCK↑, th                      | V <sub>CC1</sub> = 10 V to 15 V | 75   |     | nc   |  |

| HOW WITE, DATA IN AIRER CLOCK!, Th                       | V <sub>CC1</sub> = 4.5 V        | 150  |     | ns   |  |

| Operating free-air temperature, T <sub>A</sub>           | SN65518                         | -40  | 85  | °C   |  |

| Operating free-all temperature, 14                       | SN75518                         | 0    | 70  |      |  |

# electrical characteristics over recommended ranges of operating free-air temperature and $V_{CC1}$ , $V_{CC2}$ = 60 V (unless otherwise noted)

|                                          | PARAMETER                   |               | TEST                     | CONDITIONS                | MIN  | TYP <sup>†</sup> | MAX  | UNIT |  |

|------------------------------------------|-----------------------------|---------------|--------------------------|---------------------------|------|------------------|------|------|--|

| VIK                                      | Input clamp voltage         |               | I <sub>I</sub> = -12 mA  |                           |      |                  | -1.5 | V    |  |

| V                                        | High-level output voltage   | Q outputs     | I <sub>OH</sub> = -25 mA |                           | 57.5 | 58               |      | V    |  |

| VOH                                      | riigii-ievei output voitage | SERIAL OUT    | $V_{CC1} = 5 V$          | I <sub>OH</sub> = – 20 μA | 4.5  | 4.9              | 5    |      |  |

| Vai                                      | Low lovel output voltage    | Q outputs     | I <sub>OL</sub> = 1 mA   |                           |      |                  | 5    | V    |  |

| V <sub>OL</sub> Low-level output voltage |                             | SERIAL OUT    | I <sub>OL</sub> = 20 μA  |                           |      | 0.06             | 0.8  | v    |  |

| lіН                                      | High-level input current    |               | V <sub>CC1</sub> = 15 V, | V <sub>I</sub> = 15 V     |      | 0.1              | 1    | μΑ   |  |

| I <sub>I</sub> L                         | Low-level input current     |               | V <sub>CC1</sub> = 15 V, | V <sub>I</sub> = 0 V      |      | -0.1             | -1   | μΑ   |  |

| laa.                                     | Supply current              |               | V <sub>CC1</sub> = 4.5 V |                           |      | 1.8              | 4    | mA   |  |

| ICC1                                     | Зарріу сапені               | зирріу сипені |                          |                           |      | 2                | 5    | IIIA |  |

|                                          |                             | SN65518       | Outputs high,            | $T_A = -40^{\circ}C$      |      |                  | 12   |      |  |

| ICC2                                     | Supply current              | SN65518,      | Outputs high,            | $T_A = 0^{\circ}C$ to MAX |      | 7                | 10   | mA   |  |

|                                          |                             | SN75518       | Outputs low              | _                         |      | 0.01             | 0.5  |      |  |

<sup>&</sup>lt;sup>†</sup> All typical values are at  $T_A = 25$ °C.

SLDS004B - MARCH 1983 - REVISED MAY 1990

# switching characteristics, $V_{CC2}$ = 60 V, $C_L$ = 50 pF, $T_A$ = 25°C (unless otherwise noted)

| PARAMETER      |                                                |                         | TEST CONDITIONS          |                         | MIN MAX | UNIT |

|----------------|------------------------------------------------|-------------------------|--------------------------|-------------------------|---------|------|

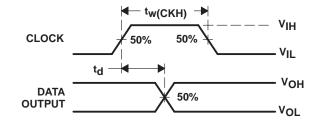

|                | Delay time, CLOCK to DATA OUT                  |                         | V <sub>CC1</sub> = 4.5 V | C <sub>L</sub> = 15 pF, | 600     | ns   |

| <sup>t</sup> d | Delay liffle, CLOCK to DATA OUT                |                         | V <sub>CC1</sub> = 15 V  | See Figure 4            | 150     | 115  |

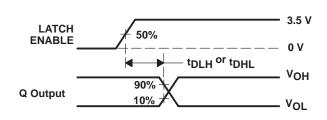

|                | Delay time, high-to-low-level Q output         | From LATCH ENABLE       | V221 - 45 V              | See Figure 5            | 1.5     | μs   |

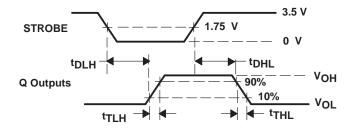

| 4              |                                                | From STROBE             | V <sub>CC1</sub> = 4.5 V | See Figure 6            | 1       |      |

| tDHL           |                                                | From LATCH ENABLE       | V 45 V                   | See Figure 5            | 0.5     |      |

|                |                                                | From STROBE             | V <sub>CC1</sub> = 15 V  | See Figure 6            | 0.5     |      |

|                | Delay time, low-to-high-level Q output         | From LATCH ENABLE       | V <sub>CC1</sub> = 4.5 V | See Figure 5            | 1.5     | μs   |

| <b>.</b>       |                                                | From STROBE             |                          | See Figure 6            | 1       |      |

| tDLH           |                                                | From LATCH ENABLE       | V <sub>CC1</sub> = 15 V  | See Figure 5            | 0.25    |      |

|                |                                                | From STROBE             |                          | See Figure 6            | 0.25    |      |

| 4              | Transition times bink to law law lovel O codes |                         | V <sub>CC1</sub> = 4.5 V | Caa Figura C            | 3       |      |

| tTHL           | Transition time, high-to-low-level Q output    | V <sub>CC1</sub> = 15 V | See Figure 6             | 1.5                     | μs      |      |

| <b>_</b>       | Transition time law to high lavel O cutou      |                         | V <sub>CC1</sub> = 4.5 V | Coo Figuro 6            | 2.5     | _    |

| tTLH           | Transition time, low-to-high-level Q output    |                         | V <sub>CC1</sub> = 15 V  | See Figure 6            | 0.75    | μs   |

#### RECOMMENDED OPERATING CONDITIONS

#### PARAMETER MEASUREMENT INFORMATION<sup>†</sup>

**Figure 3. Input Timing Waveforms**

Figure 4. Data Output Switching Times

Figure 5. Q Output Switching Times

Figure 6. Switching Time Voltage Waveforms

† For testing purposes, all input pulses have maximum rise and fall times of 30 ns.

#### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITICAL APPLICATIONS"). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER'S RISK.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, warranty or endorsement thereof.

Copyright © 1998, Texas Instruments Incorporated